ISSN: - 2306-708X

# ©2012-20 International Journal of Information Technology and Electrical Engineering Design and Analysis of Interleaved KY Converter with Reduced Voltage Stress on the Devices

<sup>1</sup>Azra Fatima and <sup>2</sup>M. S. Aspalli

<sup>1</sup>Department of Electrical Engineering, <sup>2</sup>Department of Electrical Engineering, E-mail: <sup>1</sup>a.fatima.elecengg@gmail.com, <sup>2</sup>maspalli@gmail.com

### ABSTRACT

In this work, a new interleaved Low input-High Output (LIHO) converter is proposed which comprises two KY-based converters to get a high conversion ratio. The ripple current can be reduced as we are using an interleaved strategy which reduces voltage stresses on the switches. The operational modes of the proposed converter are analyzed under varying input voltage conditions. There is various type of non –isolated converters such as buck-boost, Cuk, SEPIC, ZETA converters, etc. But the voltage gain of these converters is less compare to the proposed interleaved KY converters. The voltage gain, efficiency of the proposed converter is enhanced compared to the previous converters. The voltage stress on semiconductor devices and the ripple in the input current are reduced because of this interleaving technique. Switch with low on-state resistance is used due to which the conduction losses are reduced. Steady-state analysis and the operating principle are studied in continuous conduction mode (CCM) at ideal conditions. Simulation is also carried out in MATLAB/Simulink for the proposed interleaved KY converter.

Keywords: dc-dc converter, High voltage gain, Interleaved KY converter, Voltage stress.

### 1. INTRODUCTION

Traditional energy resources such as fossil fuels are not renewable and it is also the reason for the emission of greenhouse gases which leads to climatic changes and global warming over the earth. Hence the wind energy, solar energy, and fuel cells are utilized for power generation. As these are fluctuating in nature the voltage and power from these sources also have been fluctuating from time to time. Also, the voltage from PV panels is lower than that of the grid voltage, we have to connect the PV panels in series to achieve the required voltage [1]. In the case of PV there exist a shadow effect that cannot be neglected[2]. In the present scenario, dc-dc converters are being widely used for various purposes, Such as battery power systems, uninterrupted power supply, etc. In SEPIC dc-dc converter efficiency, voltage gain is high where the output may be greater, equal, or less than the input voltage[3].To have continuous input current for dc-dc convertor with low ripple double input source are used[4]. Various conventional dc-dc converters have high voltage gain but due to their operating conditions and the parasitic element the voltage gain of the buck-boost, Cuk, SEPIC, ZETA converters have been restricted. Also, the stress on the semiconductor device is equal to the output voltage[5-6]. The voltage gain of the converters can also be increased by using a couple-inductors in a dc-dc converter[7-10]. Thus the proper number of turns ratios must be chosen to increase the voltage gain[11-12]. But higher the turns ration reduces the efficiency and causes higher EMI noise and power loss which can be overcome by using non-isolated converters which indeed have lower size, cost, and

losses[13-16]. The newly developed converter is proposed which is named KY converters. In this converter, the voltage on the switches is less than the output voltage [17-18]. Also, the KY converters are very useful in supplying the power to the devices which will operate at low noise conditions they provide a very fast transient response which is similar to the buck converter. The output current is nonpulsating of this KY converter. But still, the voltage gain of this converter can be enhanced[19-21].

In this paper a novel high step-up interleaved dc-dc converter is presented, This converter is proposed by interleaving two modified KY converters. The voltage conversion ratio of this converter is higher than the previously developed dc-dc converter like buck-boost, Cuk, SEPIC, ZETA convertors. The overall aim of this converter is to obtain high voltage gain, high efficiency, low voltage stress on the switches, and the other semiconductor devices. The low ripple in the input current and low switching and conduction losses.

### 2. PROPOSED INTERLEVED KY CONVERTER TOPOLOGY

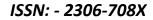

Fig1 represents a step up non-isolated interleaved dc-dc converter. In this paper, the voltage gain of the switches is less than the output voltage, and also the ripple at the output voltage are reduced and the output current is non-pulsating. As they have previously developed various converters but the voltage gain of the proposed converter is larger i.e M=1+3D/1-D (1)

The interleaved modified KY converter consists of two IGBT switches, four inductors L<sub>1</sub>, L<sub>2</sub>, L<sub>3</sub>, L<sub>4</sub>. Four diode

Information Technology & Electrical Engineering

EΕ

Journal

©2012-20 International Journal of Information Technology and Electrical Engineering

$D_1, D_2, D_3, D_4$ . Four capacitors  $C_1, C_2, C_3, C_4$ , and two output capacitor  $C_{o1}, C_{o2}$ , and the load. This converter is operated in CCM. To ease the steady-state analysis few assumptions are made:

- 1. All the parasitic parameters of the semiconductor devices are neglected.

- 2. All the semiconductor devices are in ideal condition.

- 3. The voltage of the capacitors is assumed to be constant as the size of the capacitor is considered to be large enough.

#### Fig 1 Equivalent circuit of interleaved KY converter

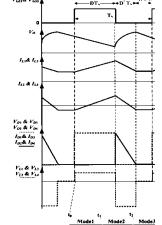

#### The interleaved KY converter operate in two modes:

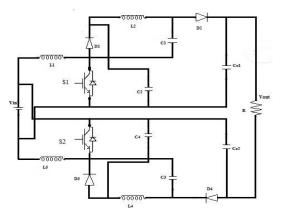

Mode 1: The time interval for this mode is  $(t_0-t_1)$ . In this mode the switches  $S_1$ ,  $S_2$  are in on state and all the four diodes  $D_1-D_4$  are in off state. As the inductors are charged from the input source, the current through the inductors rises linearly. The capacitors C1 and C3 are charged and the capacitors C2, C4 CO1, CO2 are discharged which were charged from the previous mode. The output capacitors also charge the load. Figure 2.(a) represents the current flow directions of mode 1. The voltage across the inductors are

$\begin{array}{ll} V_{L2} = V_{C2} \cdot V_{C1} & (3) \\ V_{L3} = V_{in} & (4) \\ V_{L4} = V_{C4} \cdot V_{C3} & (5) \end{array}$

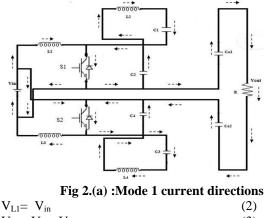

Mode 2: The time interval for this mode is (t1-t2). In this mode, both the switches are in off state and all the four diodes are in on state. As the current, though the inductors decrease to its minimum value, now the capacitors C1 and

C3 are discharged and the capacitors C2, C4, CO1, CO2, Ro are charged through the diodes D2 and D4. For the next time period, the switches S1 and S2 have turned on again which ends the mode 2. Figure 2 (b) represents the current flow direction of mode 2. The voltage across the inductors is:

#### Fig 2(b): Mode 2 current directions

| $V_{L1} = V_{in} - V_{C2}$ | (6) |

|----------------------------|-----|

| $V_{L2} = -V_{C1}$         | (7) |

| $V_{L3} = V_{in} - V_{C4}$ | (8) |

| $V_{L4} = -V_{C3}$         | (9) |

#### 3. STEADY STATE ANALYSIS OF PROPOSED CONVERTER

To ease the analysis volt second balanced law of inductor is applied for the inductors  $L_1$ ,  $L_2$ ,  $L_3$ ,  $L_4$ :

$$V_{Li} = \int_{0}^{T_{S}} (VLi) dt$$

(10)

$$V_{L1} = \int_{0}^{DT_{S}} Vin dt + \int_{DT_{S}}^{T_{S}} (Vin - Vc2) dt$$

(11)

$$V_{L2} = \int_{0}^{DTs} (Vc2 - Vc1) dt + \int_{DTs}^{TS} (-Vc2) dt \quad (12)$$

$$V_{L3} = \int_{0}^{DTS} (Vin) dt + \int_{DTS}^{TS} (Vin - Vc4) dt$$

(13)

$$V_{L4} == \int_0^{2\pi/3} (Vc4 - Vc3) dt + \int_{DTS}^{2\pi/3} (-Vc3) dt \quad (14)$$

Fig 3:Key waveforms of interleaved ky converter in ccm When KVL is applied in mode 1,the output voltage is  $Vo=V_{co1}-V_{in}+V_{co2}$  (15) Similarly in mode 2

| $V_{co1}=V_{c1}+V_{c2}$                      | (16)    |

|----------------------------------------------|---------|

| $V_{co2} = V_{c3} + V_{c4}$                  | (17)    |

| By equating equation 11, 12, 13 & 14 to zero | ,we get |

| $V_{c1} = V_{c3} = \frac{D}{1-D} V_{in}$     | (18)    |

EE Journal

. . . . .

Information Technology & Electrical Engineering

| ©2012-20 International Journa                                              | al of Information | tion Technology and | d Electrical Engin | eering |

|----------------------------------------------------------------------------|-------------------|---------------------|--------------------|--------|

| $V_{c2} = V_{c4} = \frac{1}{1-D} V_{in}$                                   | (19)              | Table 1.com         | -                  | a pro  |

| From The above equation 18 & 19<br>$V_{co1}=V_{co2}=\frac{D+1}{1-D}V_{in}$ | (20)              | Parameters          | Proposed           | Refe   |

| From equation 15 & 20 the voltage gain of the conv                         | verter is         |                     | Converter          | [3]    |

| $M = \frac{Vo}{Vin} = \frac{Vcol - Vin + Vco2}{Vin}$                       | (21)              | Voltage             | 1+3D/1-D           | n+1+   |

| Where $M = \frac{3D+1}{1-D}$                                               |                   | gain                |                    | D      |

#### Design equations of the proposed converter Inductor

As we are analyzing in CCM, so the inductor values are obtained as

$$I_{L} \ge \frac{\Delta IL}{2} \tag{22}$$

$$I_{L} = I_{D} = \frac{D(1-D)Vo}{2} \tag{23}$$

$$L_{1}=L_{3}=\frac{1}{2(1+3D)(1+D)F_{SIO}}$$

$$L_{2}=L_{4}=\frac{D(1-D)V_{O}}{1-D(1+D)F_{O}}$$

(24)

$L_2 = L_4 = \frac{1}{2(1+3D) f_{slo}}$ Capacitor

As from the voltage equations of the capacitor VC1 -Vc4 (18 & 19

) the capacitor equations are obtained. Since the charges observed by all the capacitors is equal :

$$\Delta Q = \frac{DIo}{F_S}$$

(25)

$$\Delta V c = \frac{\Delta Q}{c}$$

(26)

$$C_i = DI_0 / V_{ci} f_s$$

where  $i = 1.2..4$  (27)

### **4. VOLTAGE STRESS**

To select the proper ratings of the semiconductor devices the voltage stress of the converter is to be considered. Based on the operating principle of the proposed converter, the voltage stress on the switches and the diodes is :

| $V_{ss}1 = V_{ss}2 = 1/1 - D V_{in}$ | (28) |

|--------------------------------------|------|

| · 33 - · 35 - · · III                | ()   |

$$V_{SD(1-4)=} - 1/1 - D V_{in}$$

(29)

#### 5. COMPARISON STUDY

The proposed converter is compared with some previously developed converters in terms of voltage gain, the voltage stress on power switches, efficiency, cost, and size. The voltage stress of the proposed converter is less than these other previously developed converters for different values of the duty cycle which indeed increases the converter efficiency and hence cost of the converter is reduced. Also, the voltage conversion ration and the voltage gain of the converter are more than the previously developed converters due to the interleaving technique of two modified step-up KY converter which is proposed in this project. The number of switches used here is less compared to previously developed converters.

| Table 1.comparsion of a proposed converter with present converters |                       |               |            |

|--------------------------------------------------------------------|-----------------------|---------------|------------|

| Parameters                                                         | Proposed              | Reference     | Reference  |

|                                                                    | Converter             | [3]           | [21]       |

| Voltage                                                            | 1+3D/1-D              | n+1+(n+1)D/1- | 2(KN+1)/1- |

| gain                                                               |                       | D             | D          |

| Voltage                                                            | 1/1-D V <sub>in</sub> | M+n+1/2n+1    | M+1/2M     |

| stress on                                                          |                       |               |            |

| switches                                                           |                       |               |            |

| Number of                                                          | 2                     | 4             | 8          |

| modes                                                              |                       |               |            |

| Number of                                                          | 2                     | 1             | 2          |

| switches                                                           |                       |               |            |

| Size                                                               | Small                 | complex       | More       |

|                                                                    |                       |               | complex    |

| Efficiency                                                         | 96.6                  | 90.4          | 92.8       |

## 6. SIMULATION RESULTS

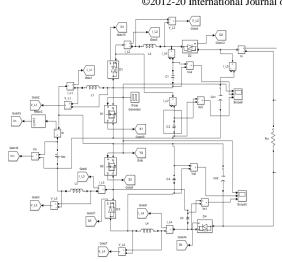

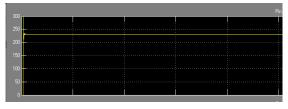

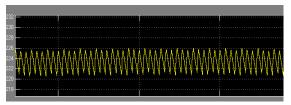

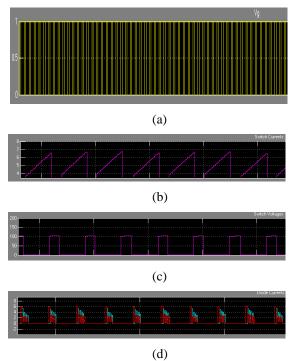

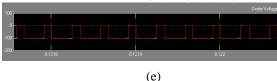

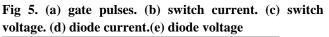

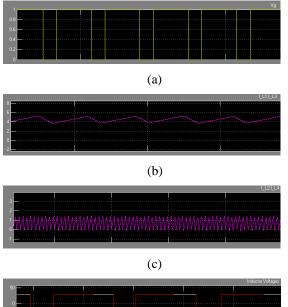

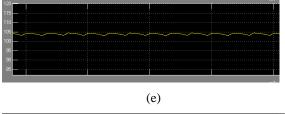

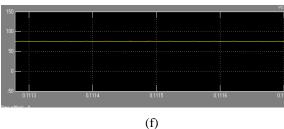

Simulations were carried out in Matlab/Simulink software. The parameter value which is used in this simulation is given in below table 1. The graphical representation of voltage, current for different components of the proposed converter is shown in fig 4& 5. The switch voltage is less the output voltage which reduces the stress on the switches, so the switches with low on-state resistance can be used. The efficiency of the proposed converter is 96.6% fig 4(c). The input power is 231W with an input voltage and current 29V and 9A represented in fig 4and the output power obtained is 225W the output voltage and current are represented in fig 4. The gate pulses are of 1V and the switch voltage Vsw and current Isw is 100V and 9A represented in fig 5. The inductor voltage and current are represented in fig 6. The capacitor voltage VC4 and VC2 are represented in fig 7.

| <b>Table2.</b> Parameter | Values | Used in | Simulation |

|--------------------------|--------|---------|------------|

|--------------------------|--------|---------|------------|

| Specifications      | Values     |

|---------------------|------------|

| Input voltage       | 29 V       |

| Output voltage      | 329 V      |

| Output power        | 225.5 Watt |

| Switching frequency | 30 kHz     |

# ISSN: - 2306-708X

©2012-20 International Journal of Information Technology and Electrical Engineering

Fig 3 Simulation Diagram

(a)

(b)

(d)

(e)

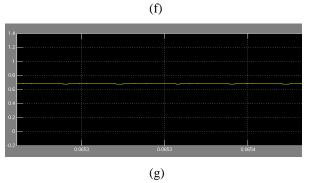

Fig 4. (a) Input power. (b) Output power. (c) Efficiency (d) input voltage. (e) input current (f) output voltage of the converter (g) output current of the converter

ITEE, 9 (5) pp. 83-88, OCT 2020

©2012-20 International Journal of Information Technology and Electrical Engineering

### 7. CONCLUSION

A new interleaved high gain step-up converter was presented in this work. By using the interleaving technique, we have reduced the voltage stress across the switches The operational modes of the proposed converter was briefly analyzed. The proposed converter is subjected to input voltage variations and the load regulation was achieved. The proposed converter consist of two switches with low on-state resistances as the voltage stress on the switches is less. The modified interleaved KY converter has high voltage gain compared the previously to developed/conventional converters and due to low ripple in the input current, this is suitable for the PV system also. They can be further enhanced by using a PV array. The converter was operated in CCM and all the semiconductor devices were analyzed in steady-state The accuracy of the proposed converter is estimated in MATLAB/SIMULINK software.

## REFERENCES

- [1] . SarwarRana, M. Nasir, and H. Abbas Khan, "String level optimization on grid-tied solar PV systems to reduce partial shading loss," *IET Renewable Power Generation*, vol. 12, no. 2, pp. 143-148, 2018.

- [2] S.H. Hosseini, M. Sarhangzadeh, M.B.B Sharifian, and F. Sedaghati, "Using PV in distribution network to supply local loads and power quality enhancement," *International Conference on Electrical and Electronics Engineering (ELECO 2009)*, pp. I-249 - I-253,2009.

- [3] H. Ardi, and A. Ajami, "Study on a high voltage gain SEPIC based DC- DC converter with continuous input current for sustainable energy applications," *IEEE Transactions on Power Electronics*, vol. 33, no. 12. pp. 10403-10409,2018.

- [4] Rw. Erickson, and D. Maksimovic, "Fundamental of power electronics," Kluwer, Norwell, MA, 2nd edition,2001.

- [5] N. Mohan, T.M. Undeland, and W.P. Robbins, " Power electronics," Wilkey New York, 2nd edition, 2003.

- [6] F. Sedaghati, SH. Mohammad Salehian, H. Shayeghi, and E. ShokatiAsl, "A configuration for double input Z-source DC-DC converters," 9th Annual Power Electronics, Drives Systems and Technologies Conference (PEDSTC), Tehran, Iran, Feb.2018.

- [7] S.H. Hosseini, F. Sedaghati, M. Sabahi, and G.B. Gharepetian, "Zero voltage switching analysis of modular isolated bidirectional DC-DC converter," *IEEE 27th Canadian Conference on Electrical and Computer Engineering (CCECE)*, Toronto, ON, Canada, May.2014.

- [8] F. Sedaghati, S.H. Hosseini, M. Sabahi, and G.B.

(d)

Fig 6. (a) gate pulses. (b) inductor current of L<sub>1</sub> and L<sub>3</sub>. (c) inductor current L<sub>2</sub> and L<sub>4</sub>.(d) voltage of inductors.

Fig 6. (a) gate pulses. (b) inductor current of L<sub>1</sub> and L<sub>3</sub>.

(c) inductor current L<sub>2</sub> and L<sub>4</sub>(d) voltage of inductors.

(e) voltage of the capacitor C<sub>4</sub>. (f) voltage of capacitor C<sub>3</sub>

ITEE Journal

©2012-20 International Journal of Information Technology and Electrical Engineering

Gharepetian,

"Analysisandimplementationofamodularisolatedzero -voltageswitching bidirectional DC–DC converter," *IET Power Electronics*, vol. 7, no. 8, pp. 2035-2049, 2014.

- [9] E. Babaei, Gh. MostafaiBaruji, H. MashinchiMaheri, A. Abbasnezhad, "A developed structure of step-up DC/DC converter by using coupled inductor and active-clamped circuit," *Journal of Operation and Automation in Power Engineering*, vol. 5, no. 1, pp. 31-42,2017.

- [10] A. Farakhor, H. Ardi, and M. Abapour, "Analysis and design procedure of a novel high voltage gain DC/DC boost converter," 8th Power Electronics, Drive Systems & Technologies Conference (PEDSTC), Mashhad, Iran, Feb.2017.

- [11] M. EskandarpourAzizkandi, F. Sedaghati, and H. Shayeghi, "Design of a new step-up DC-DC converter with high voltage gain for PV power application," *33rd International Power System Conference*, Tehran, Iran, October 2018.

- [12] M.R. Banaei, and H. AjdarFaeghiBonab, "A novel structure for single switch non-isolated transformerless buck-boost DC-DC converter," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 1, pp.198- 205,2017.

- [13] M.R. Banaei, and H. AjdarFaeghiBonab, "High-efficiency transformerless buck-boost DC-DC converter," *International Journal of Circuit Theory and Applications*, vol. 45, no. 8, pp. 1129-1150, 2017.

- [14] K.I. Hwu, and Y.T. Yau, "A novel voltage-boosting converter: KY converter," APEC 07 - Twenty-Second Annual IEEE Applied Power Electronics Conference and Exposition, Anaheim, CA, USA,2007.

- [15] K.I. Hwu, and Y.T. Yau, "KY converter and its derivatives," *IEEE Transactions on Power Electronics*, vol. 24, no. 1, pp. 128–137,2009.

- [16] K.L Hwu, K.W. Huang, and W.C. Tu, "Step-up converter combining KY and buck-boost

converters," *lET electronics letters*, vol. 47, no. 12, pp. 722-724,2011.

- [17] K.L Hwu, and Y.T. Yau, "A KY boost converter," *IEEE Transactions on Power Electronics*, vol. 25, no. ll, pp. 2699-2703,2010.

- [18] K.I.Hwu,andY.T.Yau,"TwotypesofKYBuck– Boostconverters," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 8, 2009.

- [19] K.I. Hwu, and T.J. Peng, "A novel buck-boost converter combining KY and buck converters," *IEEE Transactions on Power Electronics*, vol. 27, no. 5,2012.

- [20] A. Mostaan, H. Zeinali, S. Asghari, and A. Baghramian, "Novel high step up DC-DC converters with reduced switch voltage stress," *The 5th Power Electronics, Drive Systems and Technologies Conference (PEDSTC 2014)*, Tehran, Iran, Feb2014.

- [21] R.Ismail,Neenu B "A High Voltage Gain Interleaved Boost Converter with Dual Coupled Inductor",International Journal of Engineering Research &Technology,Vol.4,ISSUE 09, SEPTEMBER 2015

### **AUTHOR PROFILES**

**Azra Fatima** received a degree in electrical and electronics from Visvesvaraya technological university Engineering from Poojya Doddappa Appa College of Engineering Kalaburagi India, in 2018. I am Pursuing higher studies in the Power Electronics Master of Technology. Currently, I am a final year student at Poojya Doddappa Appa College of Engineering Kalaburagi India.

**Dr. Mruttanjaya Aspalli** Co-ordinator and professor of Power Electronics department Master of Technology of Poojya Doddappa Appa College of Engineering Kalaburagi India.